Docente: Prof. Mauro De Berardis

Docente: Prof. Mauro De Berardis  Docente: Prof. Mauro De Berardis

Docente: Prof. Mauro De Berardis

Lavori eseguiti dagli alunni della classe Quinta B TIEN IPSIA Teramo

Coordinamento: Prof. Mauro De Berardis, Prof. Loreto Giovannucci

Lavoro eseguito dall'alunno Mauro Ciarrocchi

Un orologio digitale è praticamente un contatore la cui struttura può essere schematizzata nel seguente modo:

figura 1

Il circuito può essere progettato

e simulato per mezzo del software in dotazione

dell’istituto.

Considerando il valore limitato della frequenza si sceglie di utilizzare contatori asincroni.

Su indicazione del docente, il prof. De Berardis, il progetto viene svolto in 2 fasi:

1^ Fase: si progetta e si simula un orologio digitale utilizzando gli strumenti generici (flip–flop JK, generatore di clock, display a 7 segmenti decodificato) di Workbench. Si verifica in questa fase la correttezza dello schema di figura 1

2^ Fase: si progetta e si simula un orologio digitale utilizzando i circuiti integrati di tipo commerciale. Si realizza in tal modo un progetto esecutivo.

1^ Fase: Per la realizzazione dei contatori vengono utilizzati flip–flop JK negative edge triggered con ingressi JK collegati tra loro in modo da funzionare come flip–flop T. Il clock viene applicato solo al primo flip–flop; il secondo flip–flop riceve il segnale di attivazione del primo, il terzo dal secondo e così via. Essendo i flip–flop di tipo negative edge triggered la commutazione avviene in corrispondenza dei fronti di discesa del segnale di clock.

In figura 2 si riporta un contatore asincrono modulo 16 (che conta da (0000) binario a (1111) binario cioè da 0 a 15 decimali) con le relative forme d’onda.

figura 2

I contatori modulo 10, modulo 6 e modulo 24 si possono realizzare a partire dal contatore modulo 16, utilizzando la linea di reset.

Contatore modulo 10: quando la catena di conteggio si trova al numero 10 (binario 1010) tutti i flip–flop vengono azzerati.

Schema da

Contatore modulo 6: quando la catena di conteggio si trova al numero 6 (binario 0110) tutti i flip–flop vengono azzerati.

Schema da

Contatore modulo 24

In questo caso il progetto è un po’ più complesso: il display delle unità si azzera quando Q3Q2Q1Q0 contano 10 decimale (1010 binario) oppure (OR) quando Q3Q2Q1Q0 contano 4 decimale (0100 binario) e Y1Y0 contano 2 decimale (10 binario). In questo ultimo caso si azzera anche il display delle decine.

Schema da

I contatori così progettati e realizzati con Workbench, vengono ridotti a sotto circuiti e collegati in cascata in maniera tale che il flip–flop più significativo di un contatore (LSB) diventi il clock del contatore successivo. Ciascun contatore è connesso ad un display a 7 segmenti già decodificato generico di Workbench. Analogamente, il clock viene fornito da un generatore di clock generico di Workbench.

Schema da

2^ Fase: si utilizzano in questa fase i circuiti integrati disponibili nelle librerie di Workbench.

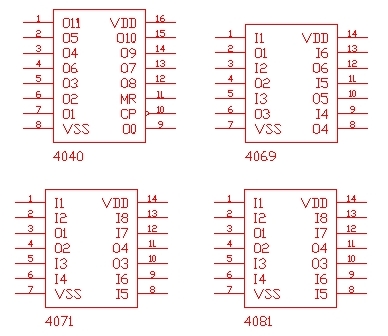

Per la realizzazione dei contatori si utilizzano i seguenti circuiti integrati della famiglia CMos della serie 4XXX :

CI 4040 contatore a 12 bit CI 4071 quadrupla porta OR a 2 ingressi

CI 4069 6 Porte NOT CI 4081 quadrupla porta AND a 2 ingressi

e si fa riferimento ai Data– sheet Fairchild.

Contatore modulo 10:

Schema da

Contatore modulo 6

Schema da

Contatore modulo 24

Schema da

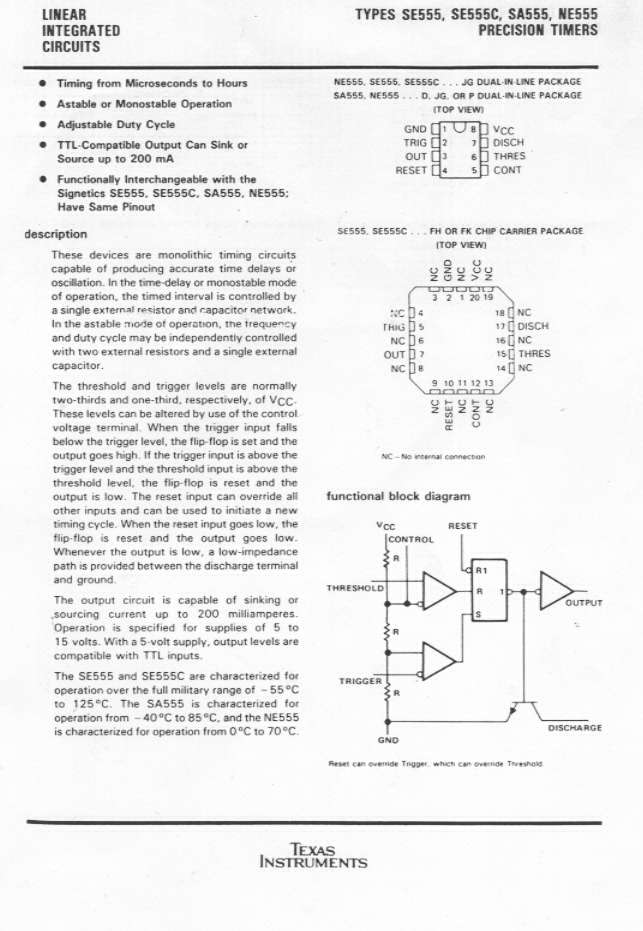

Per quel che riguarda il generatore di clok si utilizza un TIMER 555 in funzionamento astabile e si fa riferimento al Data sheet Texas Instruments.

Schema da

Essendo:

T=0.693(Ra+2Rb)C

per realizzare un segnale di clock con frequenza 1 Hz (T=1 sec.) si utilizzano i seguenti componenti: Ra=1243KOhm Rb=200 KOhm C= 1 microF

Glossario

Circuito digitale sequenziale capace di contare il numero di impulsi applicati nel tempo al suo ingresso e di fornire una indicazione numerica binaria. I contatori vengono realizzati usando i flip-flop come elementi di memoria

I contatori possono essere sincroni o asincroni. Nei primi tutti i flip-flop presentano il clock in comune ; nei secondi il clock viene applicato al primo flip-flop: tutti gli altri flip-flop ricevono il clock dal flip-flop precedente.

Simbolo

Tabella della verità

| J K | Clock | Q(i+1) | Azione |

| X X | 0 | Q(i) | Memoria |

| X X | 1 | Q(i) | Memoria |

| X X | fronte salita | Q(i) | Memoria |

| 0 0 | fronte discesa | Q(i) | Memoria |

| 0 1 | fronte discesa | 0 | Reset |

| 1 0 | fronte discesa | 1 | Set |

| 1 1 | fronte discesa | Q(i) negato | Commutazione |

La visualizzazione di informazioni trova larghissima diffusione in tutti i campi applicativi . Si considerino ad esempio i comuni orologi digitali e le calcolatrici tascabili, la strumentazione da laboratorio e portatile, le scritte luminose pubblicitarie, le bilance e le altre apparecchiature utilizzate nel settore commerciale i pannelli indicatori impiegati nel settore dell’automazione industriale,ecc..

Ovviamente, a seconda dell’applicazione, i sistemi di visualizzazione si differenziano per vari aspetti. Innanzitutto le informazioni possono essere di tipo numerico o alfanumerico ; pertanto sia la struttura del display sia il codice utilizzato per rappresentare informazione dovranno essere adeguate. Un altro fondamentale elemento discriminante è costituito dal tipo di apparecchiatura in cui deve essere inserito il display e dall’uso a cui essa è destinata; se ad esempio i visualizzatori devono consentire una lettura a distanza dovranno avere dimensioni e luminosità idonee; se invece devono essere inseriti in piccole apparecchiature con alimentazione a pila, le dimensioni e il consumo energetico dovranno essere il più possibile ridotti. In commercio sono disponibili visualizzatori di vario tipo caratterizzati da strutture e tecnologie diverse, in grado di soddisfare tutte le esigenze. Dal semplice LED, che può essere visto come visualizzatore a 1 bit, si passa ai display a 7 segmenti, a16 segmenti ( 14 segmenti oltre alla virgola e al punto), a matrice di punti ( 4 o 5 colonne x 7 righe ). Alcuni display inoltre visualizzano un solo carattere ( numerico o alfanumerico) mentre altri sono realizzati per visualizzare una stringa di carattere.

Le tecnologie, molto varie, con cui sono realizzati i visualizzatori hanno notevole importanza in quanto determinano in modo sostanziale le caratteristiche elettriche dei visualizzatori stessi e quindi dei circuiti di controllo e comando necessario

DISPLAY A LED. Fra i più diffusi sono i display a LED, prodotti in tutte le forme indicate e particolarmente, nel tipo a 7 segmenti. Ciascun elemento ( segmento o punto), che illuminandosi corre a formare il carattere, è costituito da un LED ( in certi casi più di uno); il catodo di tutti LED è collegato ad un terminale comune che, di norma, viene posto a massa. Applicando agli anodi una tensione in grado di polarizzare direttamente i rispettivi LED, si ottiene l’emissione luminosa e i segmenti o il punto appaiono accesi; scegliendo opportunamente gli elementi da accendere, si possono rappresentare i vari caratteri. Questa struttura è propria dei display a catodo comune. Altrettanto diffusi sono i display ad anodo comune,in cui ovviamente gli anodi, tutti collegati insieme vanno connessi ad un alimentazione positiva: in questi dispositivi, il comando di accensione dei vari elementi deve essere applicati ai catodi.

I vantaggi offerti dai display a 7 segmenti sono numerosi: essi possono essere realizzati in diversi colori e, anche se di dimensioni molto ridotte ( da qualche centimetro fino a 2,5mm montati con una lente) mantengano buona leggibilità: sono robusti ed affidabili; presentano livelli di tensione o corrente compatibili con quelli di molti componenti integrati per cui il circuito di comando risulta assai semplice.

Display a LED a catodo comune pilotato da 74LS48.

Lo schema in figura presenta i collegamenti essenziali fra un display a catodo comune un decoder- drive TTL commerciale, il 74LS48. I terminali di controllo (attivi bassi) LT e RBI sono fissati a livello alto; infatti essi non vengono utilizzati (come l’uscita RBO ) poiché non è richiesta altra funzione che quella della visualizzazione dei dati di ingresso. Questi ultimi vengono forniti in codice BCD e decodificati secondo la tabella riportata nei fogli tecnici . Dalla stessa tabella si desume che i segmenti si accendono quando la rispettiva linea di uscita del 74LS48 è a livello alto. Lo stadio di uscita del driver comprende una resistenza fissa (2kilohm) di limitazione della corrente. Poiché la tensione ai capi di ciascun segmento acceso del display è almeno Vf=1,6V ,la corrente erogata del driver, limitata dalla resistenza da 2kilohm, risulta molto bassa; per tanto la luminosità è assai ridotta e può non essere sufficiente.

Esistono comunque decoder-driver in grado di fornire correnti più elevate (vedi ad esempio il 9368). Altri tipi, avendo una struttura di uscita a collettore aperto (vedi 74LS49) o ad emettitore aperto ( vedi MC14511B e MC14513B), oppure altre strutture simili (vedi 74HC4511), richiedono l’inserimento di una resistenza limitatrice esterna e quindi dimensionabile, in qualche misura, dall’utente.

DISPLAY A LED AD ANODO COMUNE PILOTATO DA 74LS47.

In figura è illustrata un applicazione analoga alla precedente che però fa uso di un display ad anodo comune e di un decoder-driver con uscita open- collector attive basse (74LS47 ). L'inserimento di resistori esterni da 220ohm permette di erogare a ciascun segmento del display (considerando Vf=1,7V) una corrente di 15mA . Si tenga presente che tale valore deve essere inferiore alla massima corrente che ciascun uscita del driver può assorbire ( sinc current ), che in questo caso è 24 mA .

Il timer 555 è un circuito integrato contenente componenti analogici (transistors BJT) e digitali (flip-flop) e a molteplici applicazioni; le più importanti sono il multivibratore astabile e i l temporizzatore. In figura è riportato lo schema e tra parentesi è indicata la piedinatura

Inglese

Traduzione del data scheet

Descrizione

Questi componenti sono circuiti monolitici temporizzati capaci di produrre tempi precisi di ritardo o oscillazioni. Nel modo di operare come ritardatore o in modo monostabile, l’intervallo di tempo è controllato da un resistore esterno e una rete di capacitori. Nel modo di operare come astabile la frequenza e il duty-cycle sono controllati indipendentemente da due resistori esterni e da un singolo capacitore esterno. Il livello di threshold e di trigger sono rispettivamente 2/3 e 1/3 della Vcc. Questi livelli possono essere variati per mezzo del terminale del controllo di voltaggio. Quando l’ingresso di trigger scende sotto il livello del trigger il flip-flop è settato quindi l’uscita è alta. Se l’ingresso del trigger è superiore al livello del trigger e l’ingresso threshold è superiore al livello del threshold il flip-flop sì resetta l’uscita è bassa. L’ingresso del reset può annullare tutti gli altri ingressi è può essere usato per iniziare un altro ciclo. Quando l’ingresso del reset è basso, il flip-flop è resettato e l’uscita è bassa. Tutte le volte che l’uscita è bassa una via di bassa impedenza è prevista tra il terminale discarge e la massa. L’uscita del circuito è in grado di erogare o di assorbire una corrente di snik o di source fino ai 200 mA. Il componente funziona con una tensione che va da 5-15 Volt. Con 5 Volt i livelli di uscita sono compatibili con ingressi TTL. SE555 e SE555C sono caratterizzati per funzionare va dai –55°C ai 125°C. SA555 è caratterizzato per funzionare dai –40°C ai 85°C, NE555 è caratterizzato per il suo funzionamento che va dai 0°C ai 70°C.

Elettronica, Telecomunicazioni e

applicazioni

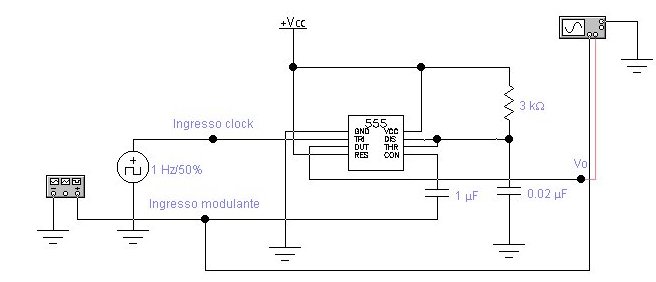

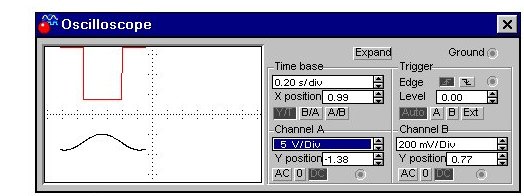

Un’applicazione importante del timer 555 è quella del modulatore a larghezza di impulsi PWM (Pulse Width Modulation).

La modulazione PWM è una tecnica di modulazione di un segnale analogico su portante impulsiva.

Con questa tecnica viene fatta variare la larghezza o durata degli impulsi in funzione del segnale modulante; mentre la frequenza dell’ampiezza degli impulsi rimangono costanti.

Lo schema del modulatore il cui funzionamento è stato verificato con il programma di risoluzione Electronics Workbench, e le relative forme d’onda sono riportate nelle figure seguenti.

Matematica

Facendo riferimento allo schema sopra disegnato, i parametri più importanti del generatore di onde quadre, possono essere così determinate: